此文探究了 Windows 与 Ubuntu(WSL2) 下使用 VScode 作为 ISE 的外部编辑器的相关方法,以实现 Verilog 代码的语法检查与格式化等功能。如有疏漏或者更好的解决方案,还望及时提出、指正。(,,•́ . •̀,,)

当然,这些内容除了部分遇到的问题外,网上均可以找到每一部分相关的教程,但我还是结合自己实践的经历,将它们整合在一起,希望可以对大家有所帮助。(●>∀<●)

整体思路

首先,需要感谢潘天蔚学长在答疑群指出的外部编辑器功能。ヾ(*′▽‘*)ノ

- 通过在 ISE 中设置外部编辑器,在 VSCode 中打开代码文件。

- 使用

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog这一 VSCode 插件调度核心功能。 - 使用

verible-verilog-format作为 Formatter 进行代码格式化。 - 使用

iverilog作为 Linter 进行语法检查。

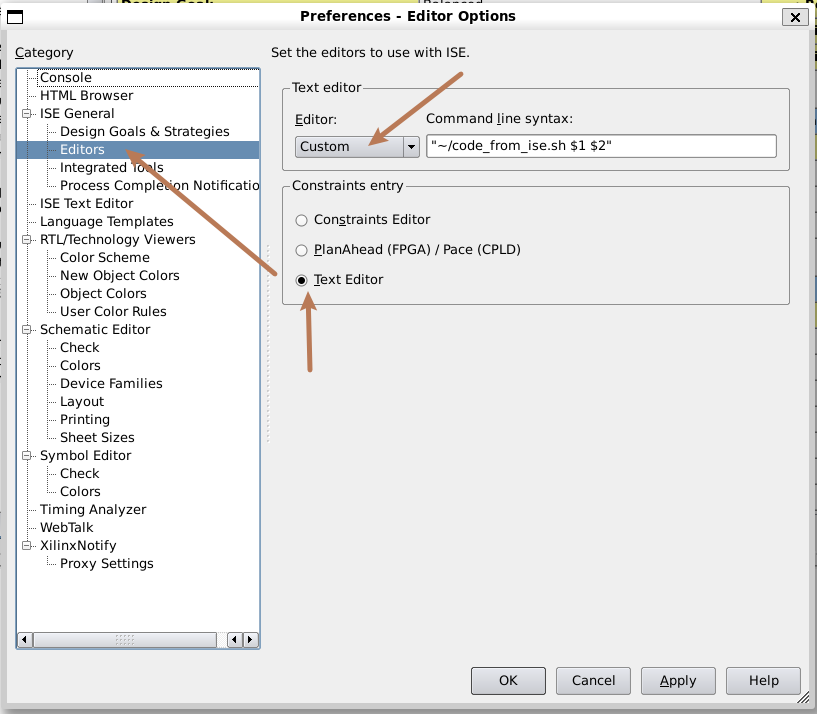

外部编辑器

在 ISE 中,依次点击 Edit -> Preferences

打开设置,进入 ISE General -> Editors 标签,将

Editor 选择为

Custom,后面的命令行是需要有针对性地进行配置的。

Windows 系统

对于 Windows 系统来说,我没有遇到很多坑点,找到

VSCode 的安装路径,比如

E:\Program Files\Microsoft VS Code\Code.exe,将其中的

\ 与

(空格)进行转义,并加上参数

-r . -r -g $1:$2 即可,如:

1 | E:\\Program\ Files\\Microsoft\ VS\ Code\\Code.exe -r . -r -g $1:$2 |

其中,

-r意为重用窗口,打开.为当前目录,-g表示打开文件并跳转到指定行号,$1和$2为 ISE 提供的类似宏的东西,分别表示文件名与行号。参考:https://blog.csdn.net/weixin_39750496/article/details/104520683(存档)

使用 WSL

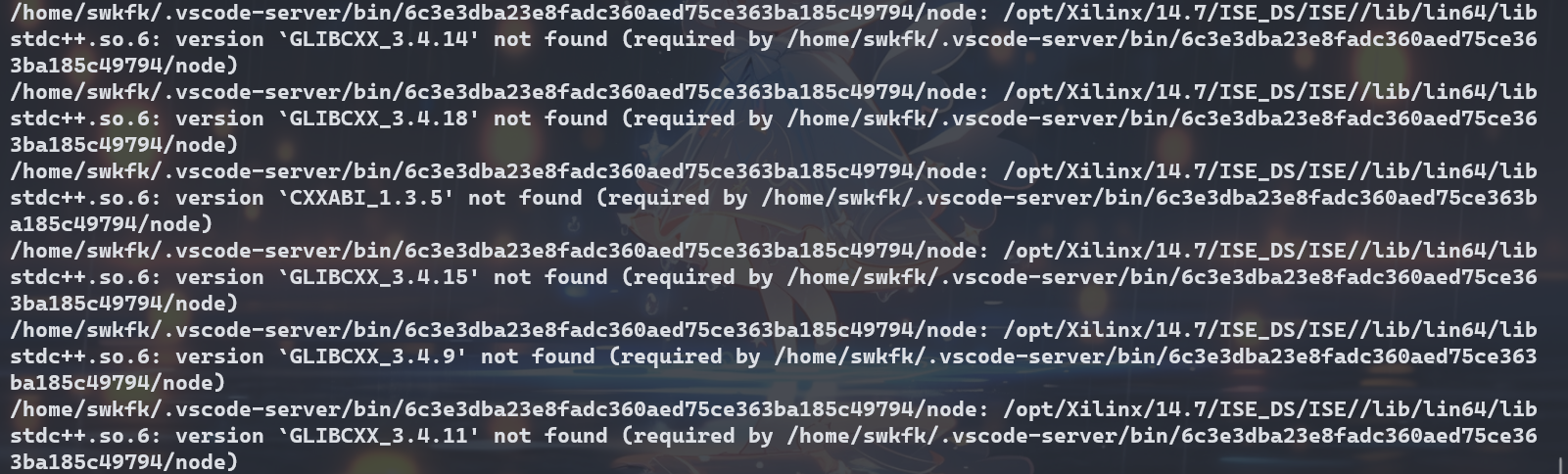

对于 Ubuntu(WSL2) 系统来说,我试图如法炮制,却遇到了如下报错:

大概就是在启动 VSCode 时,所调用的 libstdc++.so.6

的版本太低,在这里可以注意到,这个链接库的位置为 ISE

的安装路径,可以推测是启动 ISE 时覆写了 $LD_LIBRARY_PATH

导致优先加载 ISE 自带的链接库。

如果在配置时也遇到了这样的情况,我使用的解决方法如下:

首先找到系统中高版本的 libstdc++.so.6:

1 | find / -path "/mnt/*" -prune -o -name "libstdc++.so.*" -print |

上述命令排除了 /mnt 路径,因为这是 WSL

挂载本机磁盘的地方。

然后使用如下命令验证找到的库(比如

/usr/lib/x86_64-linux-gnu/libstdc++.so.6)中包含上面报错中所需要的东西:

1 | strings /usr/lib/x86_64-linux-gnu/libstdc++.so.6 | grep 'GLIBCXX' |

接着,在家目录中(或其他位置)写一个脚本,姑且叫做

code_from_ise.sh,内容如下:

1 | export LD_LIBRARY_PATH=/usr/lib/x86_64-linux-gnu:$LD_LIBRARY_PATH |

其中,第一行中间的路径应该进行相应的替换。

最后,在 ISE 的设置中写入:

1 | ~/code_from_ise.sh $1 $2 |

即可。

课程组的虚拟机

我没有进行测试,因为我电脑硬盘空间不够我装第三个 ISE 了。 ╮(๑•́ ₃•̀๑)╭

但是我觉得可以先参考 Windows 的方法试一试,如果遇到类似于在 WSL 中的报错,可以参考我的解决方法。

代码格式化

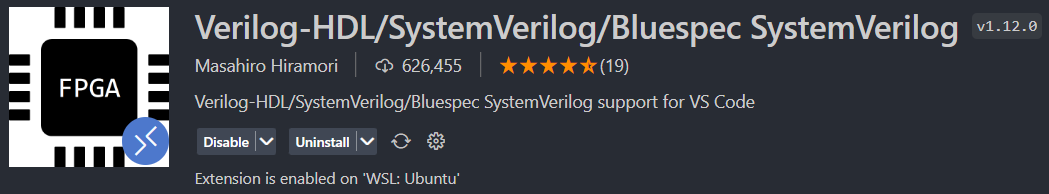

正如上面整体思路中所写,需要在 VSCode 中装一个插件:

然后从 Github 仓库中下载 verible-verilog 工具:https://github.com/chipsalliance/verible/releases/tag/v0.0-3410-g398a8505 。

Linux 如果不清楚版本的话,下载 static-x86_64

即可,一般没问题(总不至于用 ARM 架构的芯片自己却不知道吧())

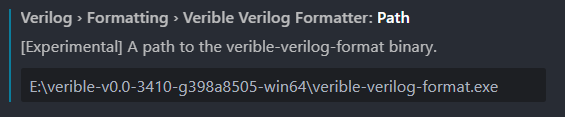

Windows

Windows 直接解压到合适的位置,并复制其中

verible-verilog-format.exe

的地址,比如:E:\verible-v0.0-3410-g398a8505-win64\verible-verilog-format.exe,填入

VSCode 的设置中:

该设置的 id 为

verilog.formatting.veribleVerilogFormatter.path,可以直接搜索。注意路径不要有空格之类的字符,把引号去掉。

并在设置中(id 为

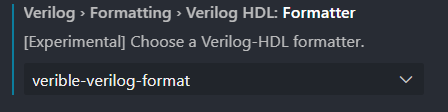

verilog.formatting.verilogHDL.formatter)将选择

verible-verilog-format 进行格式化。

Linux

将下载的文件解压,只要里面的

verible-verilog-format,将其复制到一个比较 “正式”

的路径,比如 /usr/local 中,然后在设置中将路径填为

/usr/local/verible-verilog-format 即可。

格式化选项

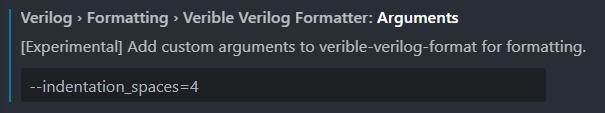

在这个设置中(id 为

verilog.formatting.veribleVerilogFormatter.arguments)可以配置自己喜欢的格式化参数:

详细的文档可以参考:https://chipsalliance.github.io/verible/verilog_format.html

比较常用的就是一个:--indentation_spaces=4,缩进使用 4

个空格。

此外,通过勾选

editor.formatOnSave设置,可以在保存时自动进行格式化。

语法检查

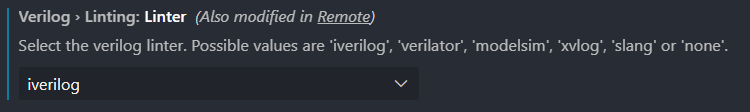

我是用 iverilog 进行语法检查,其安装并不困难,然后在设置中将 Linter

选为 iverilog (该设置 id 为 verilog.linting.linter

)。

下面,是我在使用中遇到的一个问题及解决方法。

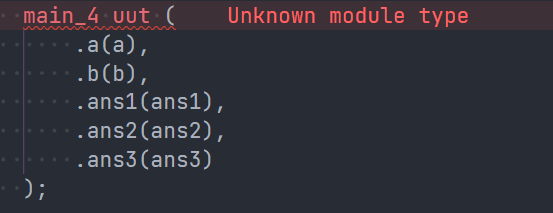

在写 test bench 时需要对模块进行例化,但是 iverilog 并不能将其识别,而会显示模块未知。

而莫名其妙的报错是让人很不爽的 <(`^′)>

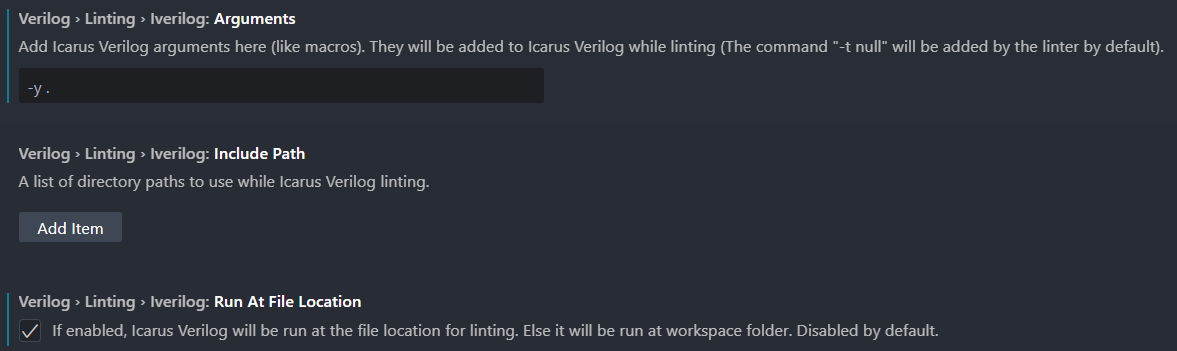

其解决方案是,在设置中给 iverilog 添加一个参数 -y .

并勾选 Run As File Location,这两个设置的 id 分别为

verilog.linting.iverilog.arguments 和

verilog.linting.iverilog.runAtFileLocation。

但是注意,待例化模块的模块名应与文件名一致,否则仍然无法识别。

诶都,有个比较蠢的办法就是拿vsc当编辑器,写完了copy到ise里跑,比较方便,我感觉用着还比较舒服,不过有个缺点就是这样子就要频繁切屏

这样是不是干脆就可以用 VCS 或者 iverilog+gtkwave 这样的,可以在命令行搞定编译、仿真的工具链呢,前者就没 ISE 的事了,后者只消最后放进 ISE 确保一下没有差异?