提示:这篇文章即将在作者的博客上发布,敬请期待。

iverilog和gtkwave均为跨平台开源工具,进行配置后本教程同样适用于windows和linux平台

由于在Mac端无法使用ISE和VCS,我在搜索后找到了iverilog和gtkwave作为Mac端原生编译和运行调试verilog的工具,在此做一个分享(编辑器采用VSCode)。

环境配置

首先,你需要homebrew来安装这些工具,如果你没有安装homebrew可以参考这个博客。

进入terminal后输入以下命令

- 安装iverilog:

1 | brew install icarus-verilog |

- 安装gtkwave:

1 | brew install caskroom/cask/gtkwave |

编写和运行verilog代码

确认已经安装好需要的工具后,我们可以开始编写verilog代码了。(此处以教程中时序电路练习_1 编号:1109-400为例)

首先,在vscode中新建一个目录,目录中新建文件counter.v用于编写counter模块

vscode中可以自己搜索并安装verilog相关扩展提供代码补全和高亮,我目前使用的是

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog

不是太好用

counter.v 内容(并非最佳实现):

1 | module counter( |

编写完成后,在目录中新建counter_tb.v 用于编写testbench

counter_tb.v 内容:

1 | module counter_tb; |

现在,我们需要在terminal手动进行编译,生成波形文件,并用gtkwave查看生成的波形。

编译

在terminal输入:

1 | iverilog -o wave counter.v counter_tb.v |

-o指定生成文件的名称(wave),后面的参数表示编译的源文件,完成编译后,可以看到目录中多出了wave文件

生成波形文件

输入:

1 | vvp -n wave -lxt2 |

运行后,可以看到目录产生了wave.vcd文件

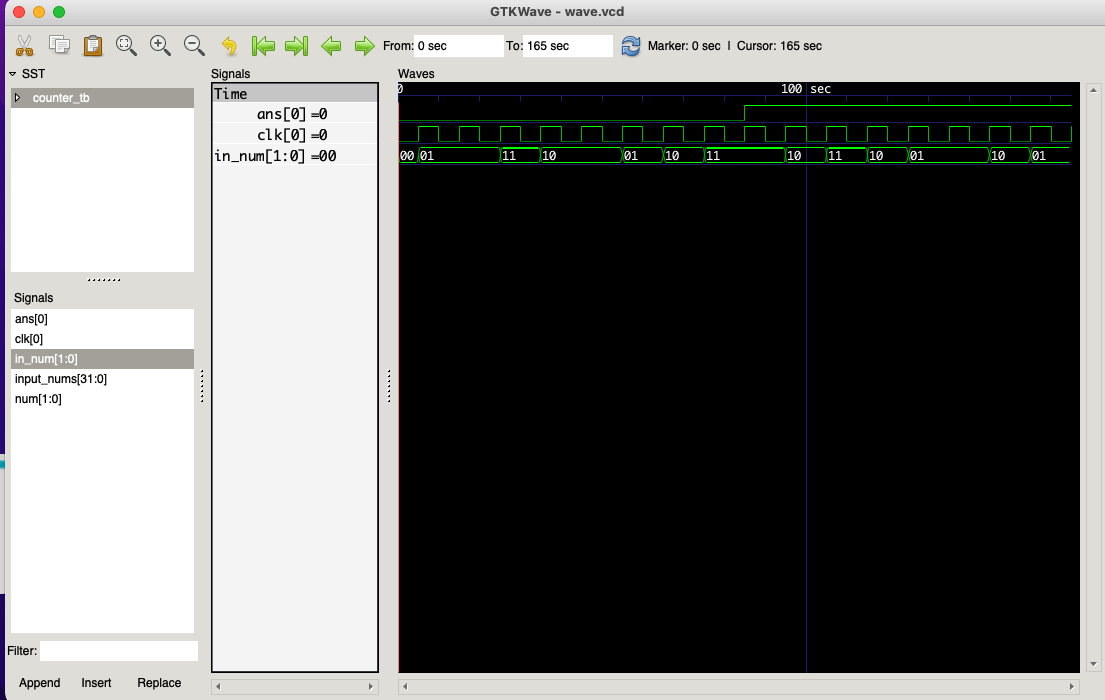

用gtkwave查看波形

gtkwave可以直接打开软件,打开波形文件查看。

更推荐的做法是,在terminal输入gtkwave wave.vcd

如图,gtkwave中就可以查看仿真的波形,可以看到和预想的结果一致。

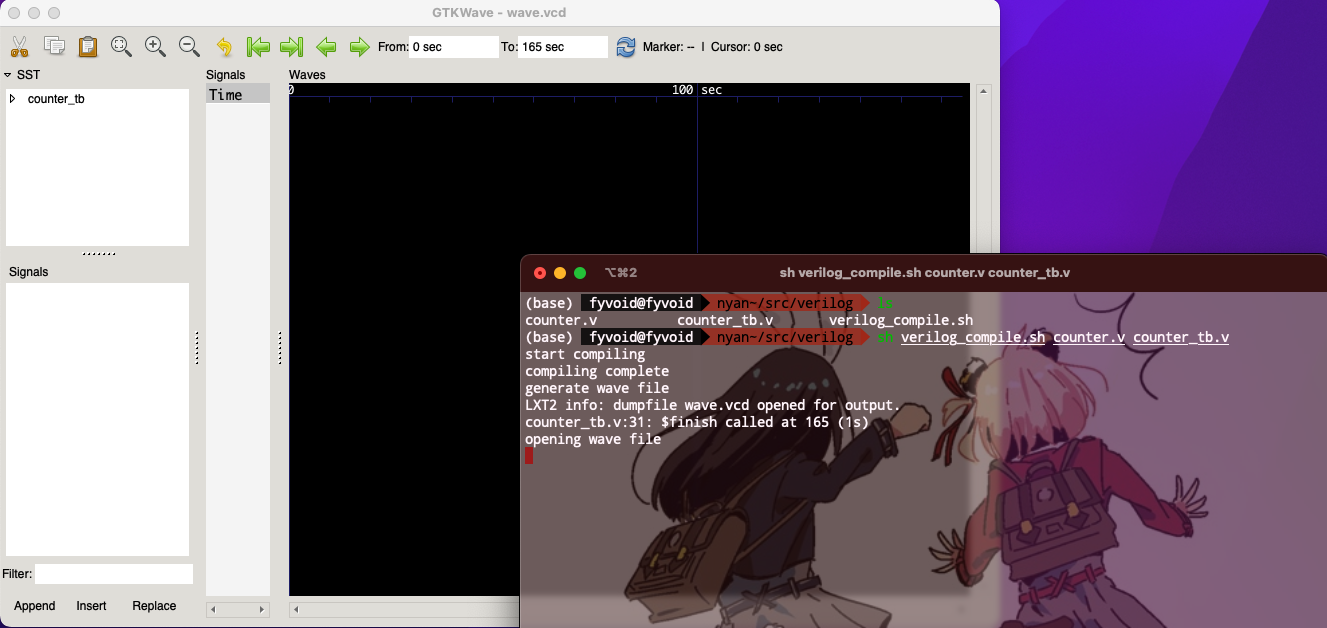

偷懒

程序员诞生的目的就是为了偷懒。

既然我们需要多个控制台命令完成这个过程,不如写一个shell脚本来自动化这个过程

在目录新建一个verilog_compile.sh 文件,内容为:

1 | echo 'start compiling' |

通过在终端将这个shell脚本当作编译命令使用,可以直接完成上一节的所有过程。

也可以修改shell脚本中相关部分,直接在vscode中运行shell脚本。

也可以修改shell脚本中相关部分,直接在vscode中运行shell脚本。

很棒的尝试!iverilog+gtkwave确实是非常轻量级,也非常方便的仿真verilog的方法。

但需要注意的是,此种工具链的仿真行为并不保证与课程组的评测所采用的工具链相同,因此若出现问题请在ise/vcs中仿真进行检查,确保本地代码编写无误

另外,若安装gtkwave的时候报错,可以直接brew install gtkwave即可,而直接双击打开wave.vvd波形文件会直接打开gtkwave,不需使用命令行,若使用命令行报错的同学也可以尝试直接双击该波形文件

看起来像是你调用命令的目录下没有读取文件的权限,你可以更换到其他目录尝试一下 例如:

1 | ~ cd |

同学您好,我已经安装好了iverilog和gtkwave,但运行以上代码的时候报错了,请问您知道要怎么解决吗?

同学您好,我已经安装好了iverilog和gtkwave,但运行以上代码的时候报错了,请问您知道要怎么解决吗?